Xylon offers a complete logicBRICKS IP Suite for implementing High-Dynamic Range (HDR) Image Signal Processing (ISP) pipelines in embedded designs based on programmable Xilinx FPGA and Adaptable SoC devices.

Key IP cores, the

logiISP-UHD ISP pipeline and the

logiHDR HDR pipeline, support parallel processing of multiple video inputs, resolutions up to 7680x7680 (including the popular 4K2Kp60 video resolution), merging of two or three exposures, parallel pixel processing and different pixel formats. These IP cores for programmable logic implementations are supplemented with AWB and AE software libraries that use video statistics data collected at the video inputs, software drivers, demo applications, reference SoC designs, and bit-accurate C models. Both IP cores are updated for use with the Xilinx Vitis™ Unified Software Platform.

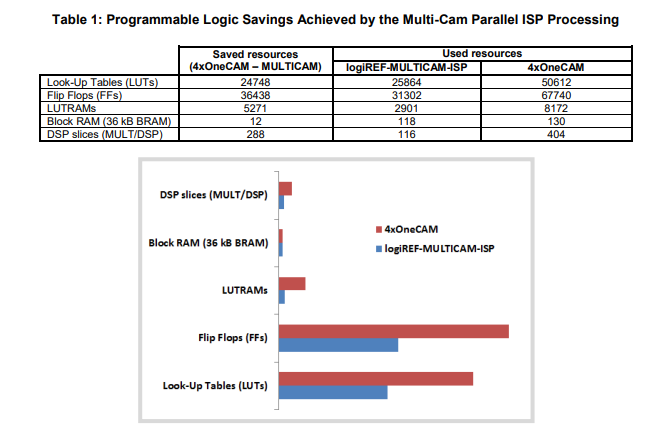

In comparison to simple instantiation of multiple ISP pipelines within a single programmable device, Xylon's multi-channel ISP pipelines allow for tremendous savings of up to 50% of valuable programmable logic. The following image demonstrates programmable logic savings achieved in the

logiREF-MULTICAM-ISP reference design.

Click Photo to Enlarge!

Click Photo to Enlarge! In comparison to simple instantiation of multiple ISP pipelines within a single programmable device, Xylon's multi-channel ISP pipelines allow for tremendous savings of up to 50% of valuable programmable logic. The following image demonstrates programmable logic savings achieved in the logiREF-MULTICAM-ISP reference design.

Xylon's logicBRICKS IP cores are very configurable and the HDR ISP pipeline can be tuned in different ways:

- define the structure of the HDR ISP pipeline through the Xilinx Vivado GUI

- recombine different processing stages in various custom pipelines

- control the implemented pipeline by software

- software libraries can use statistics data, i.e. AW and AE algorithms