> 15. October 2015, Zagreb

(Croatia) – Xylon announces the logiJPGD Multi-Channel Motion JPEG Decoder IP core compliant to the ISO/IEC 10928-1 baseline DCT JPEG standard and optimized for Xilinx® Zynq®-7000 All Programmable SoC and FPGA devices. Even though the logiJPGD IP core can be used in any still image and MJPEG video decompression application, it is the best-suited for multi-channel video over IP applications, such as multi-camera Advanced Driver Assistance (ADAS), machine vision and surveillance.

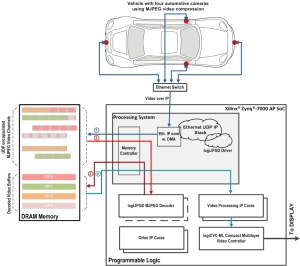

The figure illustrates an example multi-camera Advanced Driver Assistance (ADAS) application using Ethernet as an in-vehicle networking technology and the Xilinx Zynq-7000 AP SoC as a video processor. Four video cameras installed around the vehicle's perimeter encapsulate the MJPEG compressed video in the Ethernet UDP packets and stream them through a network switch and a single Ethernet cable towards the Xilinx Zynq-7000 AP SoC in a non-guaranteed order.

(Click to Enlarge!)

(Click to Enlarge!)

In order to ensure the maximum data throughput and the minimum CPU load, the Ethernet UDP IP software stack runs only a basic packet analysis and stores the encapsulated UDP packets in physically scattered memory buffers implemented in the DRAM memory (1). The logiJPGD IP core’s scatter-gather DMA fetches only the video payload from the scattered Ethernet UDP packets and does the MJPEG video decompression (2). The uncompressed video is stored in contiguous video frame buffers within the DRAM memory (3) from where it can be fetched (4) for further video processing or video display.

Key features:

• Supports Xilinx® Zynq®-7000 All Programmable SoC and 7 series FPGA families

• Compliant with the Baseline Sequential DCT mode of the ISO/IEC 10918-1 JPEG standard

• Works with up to four HD video streams simultaneously

• Keeps up the exact video input frame rates to ensure smooth playback

• Video input/output resolutions up to 2048x2048

• Supported pixel formats: YUV 4:2:0 and YUV 4:2:2

• High data throughput of 2 pixels/clock, i.e. 200MPix/sec when running at 100 MHz

• Available IP core deliverables for Xilinx Vivado® and ISE® Design Suites

• IP deliverables include software driver, documentation and technical support

• Reference design for the Xilinx ZC702 Evaluation Kit available on request

|

The logiJPGD reference design can be used as a starting point to evaluate and develop Xilinx-based MJPEG video processing embedded systems. Please submit your request for evaluation at info@logicbricks.com.

|